# 応用電力変換工学

## 第7回 パワーデバイス

平成20年11月12日

### 概要

- パワーエレクトロニクスとパワーデバイス

- パワーデバイスの種類と基本構造

- 耐圧設計

- 半導体材料のパワーデバイス性能指標

- Si, SiC

- パワーダイオードの動向

- パワーMOSFETの動向

- IGBTの動向

- おわりに

## パワーデバイスに求められるもの

- パワーエレクトロニクス

- 電気利用範囲の拡大

- 静止器化

- 電気駆動化

- 機能向上

- 制御・多機能化

- メンテナンスレス

- 効率向上

- スイッチング動作

- 最適動作点

- パワエレ機器の効率向上

- 適用範囲の拡大

- 低電圧 → 高電圧

小電流 → 大電流

- 5,3,3,1.7V → 1500V, 2.5kV, 500kV

- $\mu$ A → kA

- IT機器電源 → 送配受電機器

- 低コスト化

- 小型化

- 高信頼化

2008/11/12

応用電力変換工学

3

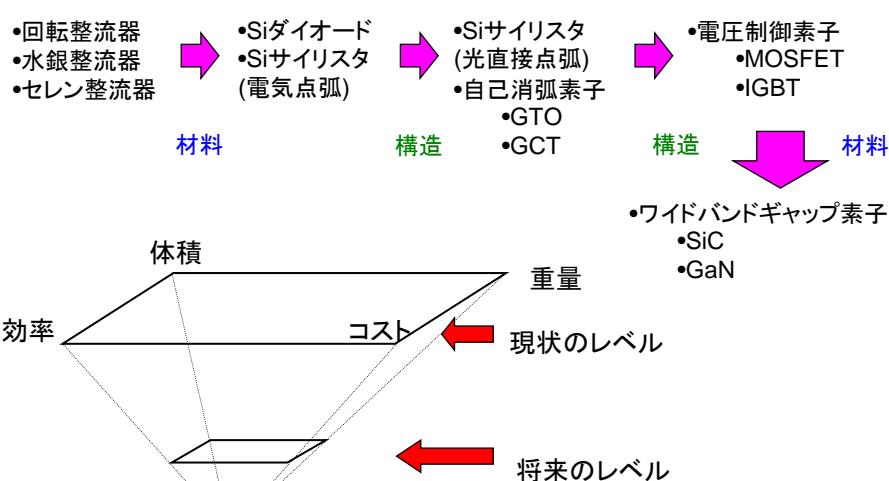

## パワースイッチングデバイスの変遷

2008/11/12

応用電力変換工学

4

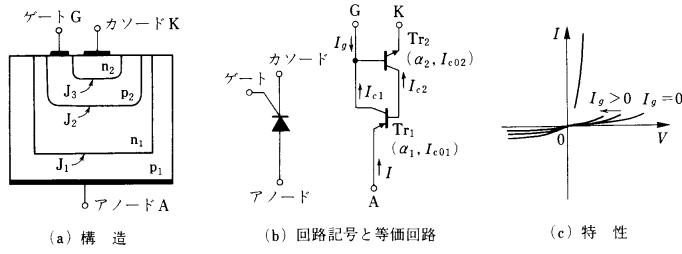

## パワースイッチングデバイスの基本構造1

図 8.5 SCR

松波, 吉本,

半導体デバイス,

共立出版より

### • サイリスタ

#### - ターンオン

- 接合J<sub>3</sub>を順バイアス

- 注入された電子が, 高電界のかかっているJ2で加速, なだれ破壊

#### - ターンオフ

- AK間電圧を小さくする, 電圧の極性を反転

2008/11/12

応用電力変換工学

5

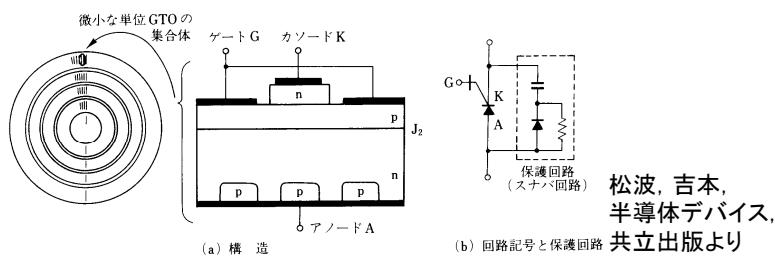

## パワースイッチングデバイスの基本構造2

図 8.7 GTO

松波, 吉本,

半導体デバイス,

共立出版より

### • GTOサイリスタ

- アノードは短絡エミッタ構造

- 阻止状態で, 急峻な電圧変化によるターンオンを防ぐ

- オン時はJ<sub>2</sub>近傍にキャリアが蓄積

- ターンオフ時にJ<sub>2</sub>のキャリアを引き抜く

- 微細GTOの集合

2008/11/12

応用電力変換工学

6

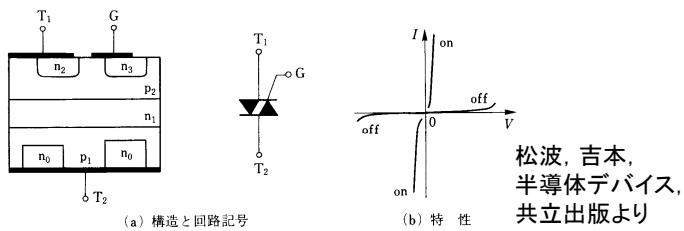

## パワースイッチングデバイスの 基本構造3

図 8.9 トライアック

### • トライアック

#### – 両方向性の素子

- ゲート電圧が正, 負のどちらでもターンオン

- $T1 > T2, Vg > 0, p2 \rightarrow n2$  の電流が流れ, サイリスタ動作  $p1n1p2n2$

- $T1 > T2, Vg < 0, p2 \rightarrow n3$  の電流が流れ, サイリスタ動作  $n3p2n1p1$

- $T1 < T2, Vg > 0$ , トランジスタ  $n2p2n1$  の  $n2p2$  順バイアス,  $n1$  に電子注入,  $p2n1p1n0$  オン

- $T1 < T2, Vg < 0$ , トランジスタ  $n3p2n1$  の  $n3p2$  順バイアス,  $n1$  に電子注入,  $p2n1p1n0$  オン

2008/11/12

応用電力変換工学

7

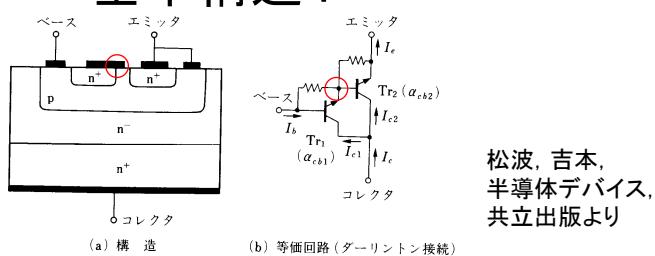

## パワースイッチングデバイスの 基本構造4

図 8.10 パワートランジスタ

### • パワーバイポーラトランジスタ

- パワー用として耐圧, 電流容量, 放熱を向上

- コレクタ領域不純物濃度を下げ耐圧向上

- N+層を作りできるだけ低抵抗化

- ダーリントン接続構造 ○部

2008/11/12

応用電力変換工学

8

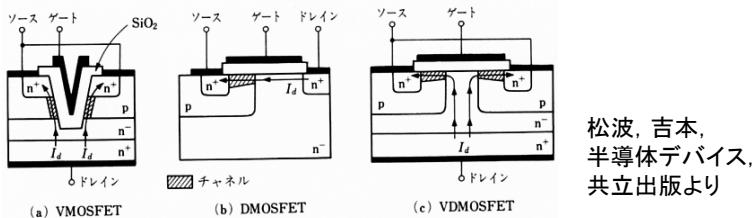

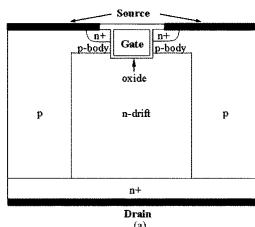

## パワースイッチングデバイスの 基本構造5

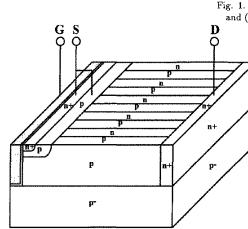

図 8.11 パワー MOSFET

松波, 吉本,

半導体デバイス,

共立出版より

### • パワーMOSFET

- 熱暴走しない

- 短チャネル化で抵抗抑制

- V-shaped grooved MOSFET

- 二重拡散(double diffused) MOSFET 電流横向き

- 縦型(vertical DMOSFET) 電流縦向き, 基板全体使用, 大電流化

2008/11/12

応用電力変換工学

9

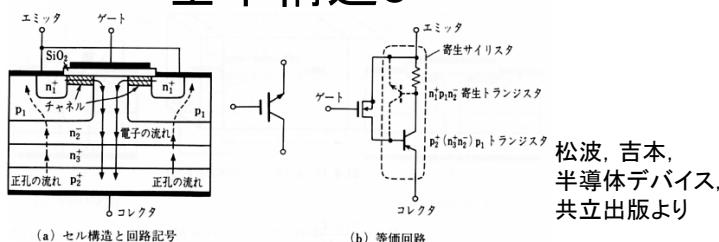

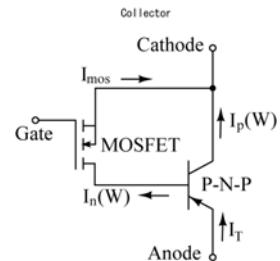

## パワースイッチングデバイスの 基本構造6

図 8.13 IGBT

松波, 吉本,

半導体デバイス,

共立出版より

### • 絶縁ゲートバイポーラトランジスタ(IGBT)

- VDMOSFETのドレインn+と, ドレインの金属電極間にp+領域を形成

- NチャネルMOSFETがバイポーラトランジスタp2+(n3+n2-)p1をオン

- 少数キャリア注入による抵抗低減

- p2+(n3+n2-)p1n1+に寄生サイリスタ構造を持つ

- ラッチアップ動作 危険

2008/11/12

応用電力変換工学

10

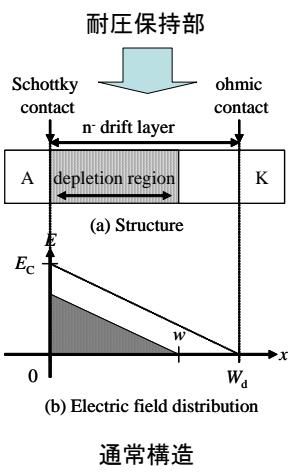

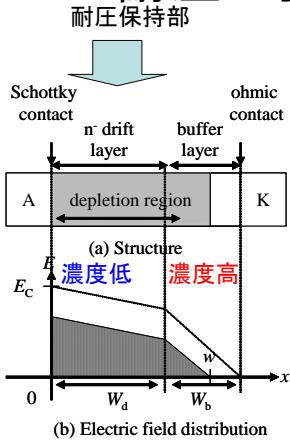

## パワーデバイスの耐圧保持部1

- 電界と電荷分布

- ポアソンの式

$$\frac{d^2V(x)}{dx^2} = \frac{dE(x)}{dx} = -\frac{\rho(x)}{\epsilon_s}$$

- 一様な不純物濃度分布

$$\rho(x) = \text{const} = -eN_d$$

- 電圧分布

$$V(x) = -\frac{eN_d}{2\epsilon_s} (x - w)^2$$

$$w = \sqrt{\frac{2\epsilon_s}{eN_d}} \sqrt{V_{ka}}$$

2008/11/12

応用電力変換工学

11

## パワーデバイスの耐圧保持部2

- 耐圧と絶縁破壊電界

$$V_{bd} = \frac{eN_d}{2\epsilon_s} W_d^2 = \frac{\epsilon_s}{2eN_d} E_c^2$$

- 耐圧とオン抵抗

- 耐圧の二乗に比例

$$R_d = \frac{W_d}{\mu eN_d A} = \frac{4V_{bd}^2}{\mu \epsilon_s A E_c^3}$$

- 耐圧と抵抗のトレードオフ

- 不純物濃度減少 → 耐圧上昇 → 抵抗増大

- 抵抗減少 → 不純物濃度上昇 → 耐圧低下

2008/11/12

応用電力変換工学

12

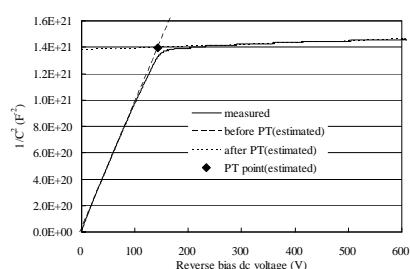

## パンチスルー構造による 耐圧とオン抵抗の改善

2008/11/12

応用電力変換工学

- 電界分布

- 不純物濃度に依存

- オン抵抗

- 通常構造の84%

$$R_{d-min} = \frac{27}{8} \frac{V_{bd}^2}{\mu \epsilon_s A E_C^3}$$

- パンチスルー電圧

$$V_{pt-opt} = \frac{e W_d^2}{2 \epsilon_s} \frac{2 \epsilon_s}{e W_d^2} (W_d E_C - V_{bd})$$

$$= W_d E_C - V_{bd} = \frac{1}{2} V_{bd}$$

13

## パワーデバイス用途における 半導体材料の性能指標-1

- Johnson figure of merit (JFOM)

- 低電圧, 低周波トランジスタ向き

$$JFOM = \frac{E_c v_s}{2\pi}$$

- $E_c$ :絶縁破壊電界,  $v_s$ :飽和ドリフト速度

- Keyes figure of merit (KFOM)

- トランジスタのスイッチ動作における熱的制約を考慮

$$KFOM = \lambda \left[ \frac{c v_s}{4\pi\epsilon} \right]^{1/2}$$

- $c$ :光速,  $\epsilon$ :半導体の誘電率,  $\lambda$ :熱伝導度

B.J. Baliga, "Power semiconductor device figure of merit for high-frequency applications", IEEE EDL Vol.10, No.10, pp.455-457, 1989.

2008/11/12

応用電力変換工学

14

## パワーデバイス用途における半導体材料の性能指標-2

- Baliga figure of merit (BFOM)

- 導通損を最小化する材料パラメータ

$$BFOM = \varepsilon \mu E_G^3$$

•  $E_G$ :半導体のバンドギャップ

- Baliga high frequency figure of merit (BHFFOM)

- 周波数の次元で表される

- 高周波スイッチング能力

$$BHFFOM = \frac{1}{R_{on,sp} C_{on,sp}} = f_B$$

•  $R_{on,sp}$ :固有オン抵抗,  $C_{on,sp}$ :固有静電容量

B.J. Baliga, "Power semiconductor device figure of merit for high-frequency applications", IEEE EDL Vol.10, No.10, pp.455-457, 1989.

2008/11/12

応用電力変換工学

15

## パワーデバイス用途における半導体材料の性能指標-3

表1. ワイドバンドギャップ半導体材料の物性定数

Physical properties of wide band gap semiconductor materials

| 材 料                                    | ダイヤモンド            | GaN                          | 4H-SiC            | 6H-SiC            | 3C-SiC            | GaAs              | Si                |

|----------------------------------------|-------------------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| バンドギャップ<br>(eV)                        | 5.47              | 3.39                         | 3.26              | 2.93              | 2.23              | 1.43              | 1.12              |

| 電子移動度 $\mu_n$<br>(cm <sup>2</sup> /Vs) | 2,200             | 900                          | 1,000/850         | 80/400            | 800               | 8,500             | 1,400             |

| 正孔移動度 $\mu_p$<br>(cm <sup>2</sup> /Vs) | 1,600             | 150                          | 115               | 90                | 40                | 400               | 600               |

| 絶縁破壊電界強度 $E_b$<br>(V/cm)               | $1 \times 10^7$   | $3.3 \times 10^6$            | $2.5 \times 10^6$ | $2.8 \times 10^6$ | $1.2 \times 10^6$ | $4.0 \times 10^6$ | $3.0 \times 10^6$ |

| 熱伝導度 $\lambda$<br>(W/cmK)              | 20                | 2.0                          | 4.9               | 4.9               | 4.9               | 0.5               | 1.5               |

| 飽和速度 $v_{sat}$<br>(cm/s)               | $2.7 \times 10^7$ | $2.7 \times 10^7$            | $2.2 \times 10^7$ | $1.9 \times 10^7$ | $2.0 \times 10^7$ | $2.0 \times 10^7$ | $1.0 \times 10^7$ |

| 誘電率 $\epsilon$                         | 5.5               | 9.0                          | 9.7               | 9.7               | 9.7               | 12.8              | 11.8              |

| パルク成長                                  | △                 | ×→△                          | △→○               | △→○               | ×→△               | ○                 | ○                 |

| エビ成長                                   | △                 | ×→△                          | △→○               | △→○               | ×→△               | ○                 | ○                 |

| BM (対 Si)                              | 27,128            | 653                          | 340               | 191               | 30                | 16                | 1                 |

| BHFM (対 Si)                            | 1,746             | 78                           | 50                | 25                | 9                 | 11                | 1                 |

| デバイスの種類                                | μエミッタ<br>パワー素子    | 青色発光素子,<br>高周波素子,<br>横型パワー素子 | 縦型パワー素子           | GaN用基板            | 中容量<br>パワー素子      | 高周波素子             | 全般                |

GaAs : ガリウム砒素

性能指標:  $BM = \epsilon \mu_n E_b^3$ ,  $BHFM = \mu_p E_b^2$

○:パワーデバイスとして広く使われているレベル    ○:使い始められるレベル    △:研究報告はあるがまだ使えないレベル    ×:使い物にならないレベル

四戸, 「SiCパワーデバイス」, 東芝レビュー, vol.59, no.2, pp.49-53, 2004.

2008/11/12

応用電力変換工学

16

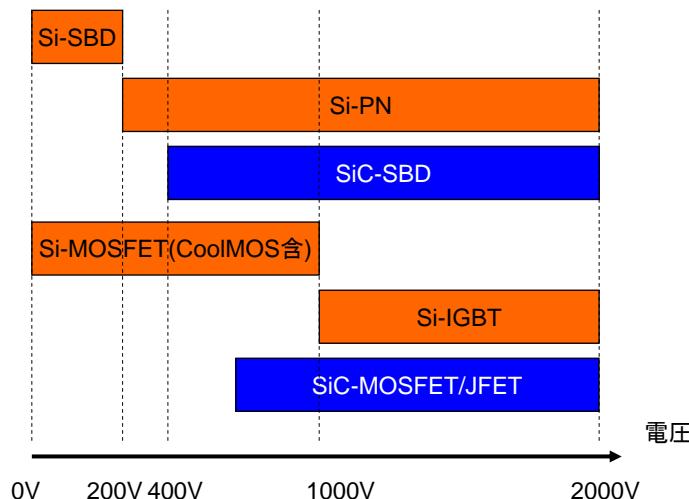

## パワーデバイスの適用領域

2008/11/12

応用電力変換工学

17

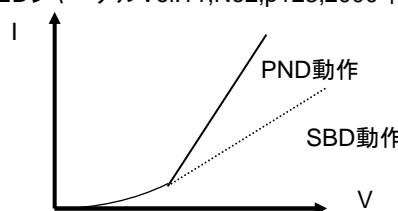

## ダイオードの高性能化

- 高耐圧化

- 他デバイスの高耐圧化に対応

- ガードリングによる電界緩和

- 導通損失の低減

- 高耐圧化とのトレードオフ

- ガードリングの有効利用

- スイッチング損失の低減

- 逆回復電流の低減

- 多数キャリアデバイス化

- 寄生インダクタンスとの共振

- 低ノイズ化

- 急峻なdv/dtによるノイズ

- ソフトリカバリー化

2008/11/12

応用電力変換工学

18

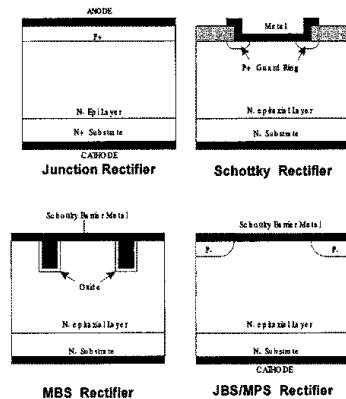

## ダイオードの高耐圧化 ハイブリッド構造

図4 SiCパワーダイオードの模式断面図

Fig. 4 Schematic cross-sections of SiC power rectifiers.

FEDジャーナルVol.11, No2, p107, 2000年.

2008/11/12

応用電力変換工学

- PN接合ダイオード

- ワイドバンドギャップ半導体

- GaNは拡散長短い

- 伝導度変調難しい

- ショットキーバリアダイオード

- 高耐圧化により抵抗増大

- ハイブリッド構造化

- 接合障壁ショットキー (JBS)・PiN/ショットキーミックス(MPS)ダイオード

- MOS障壁ショットキー (MBS)ダイオード

19

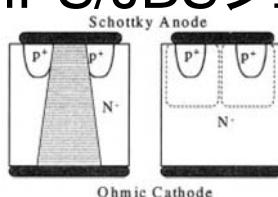

## MPS/JBSショットキーダイオード

図3 MPSダイオードの正方向オン状態電流はショットキーフィルムを通じて流れ(左)、逆方向漏れ電流は隣接するp+グリッドからの空乏層によって制限される(右)。

Fig. 3 MPS diode forward on-state current flows through the Schottky anode (left), while reverse leakage current is limited by depletion from adjacent p+ grids (right).

FEDジャーナルVol.11, No2, p123, 2000年.

2008/11/12

応用電力変換工学

- MPS構造

- ショットキ領域

- P+注入領域

- オン電圧

- ドリフト層抵抗

- ショットキ障壁高さ

- p+領域の面積比

- 電圧降下が増大した場合p+領域がpn接合として動作

- 逆バイアス条件

- P+注入領域から空乏層が伸展する

- ショットキ領域の漏れ電流を制限

- 高温動作時の漏れ電流制限に効果的

20

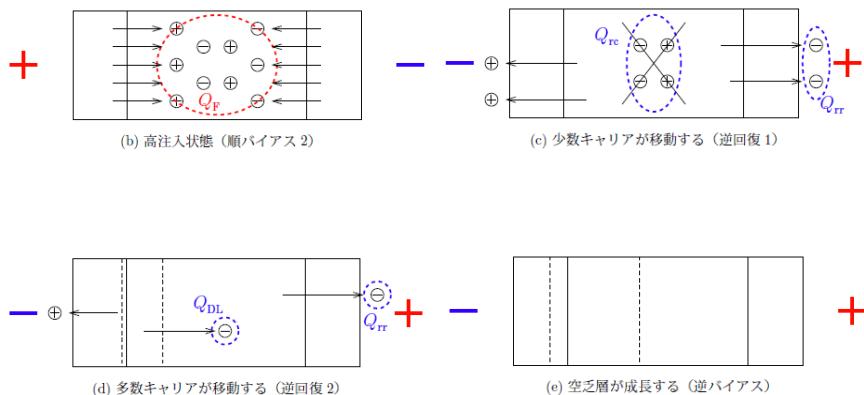

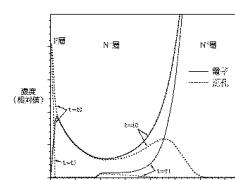

## PN接合ダイオードの逆回復現象

2008/11/12

応用電力変換工学

21

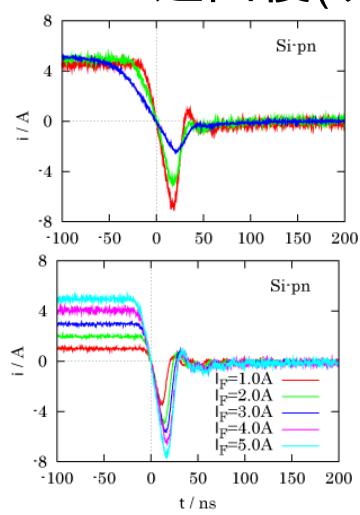

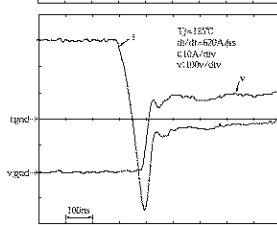

## PNダイオードの逆回復(リカバリー)特性

- ダイオードの逆回復現象

- 順バイアス

- n-層はキャリア注入により飽和する

- 注入量はIFに比例

- 逆バイアス電圧印加

- 蓄積された過剰キャリアが接合部を基点として排出

- 再結合でキャリアが消滅するまで流れる

- $di/dt$ と共に電流ピーク $IrM$ , 電荷量 $Qrr$ 増加する

- 再結合電荷量が減少

- IFに比例して $Qrr$ が増加する

2008/11/12

応用電力変換工学

22

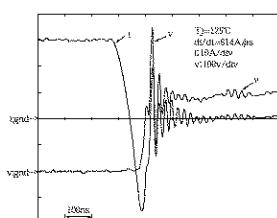

## PNダイオードの ファスト・ソフトリカバリー

図4 当社従来品

FRD

図5 開発品

日本インターNews,vol.26,no.2,pp.10-11,2000.

2008/11/12

応用電力変換工学

23

図3 逆回復動作でのダイオード内部のキャリア状態解析例

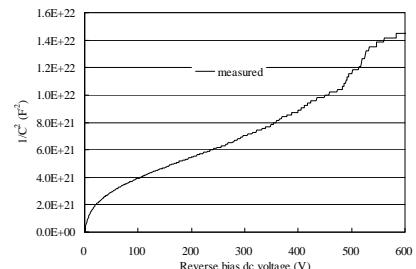

## ダイオードの特性 端子間容量

1/C<sup>2</sup> - V 特性

SiC SBD パンチスルータイプ

Si PiN 非パンチスルータイプ

2008/11/12

応用電力変換工学

24

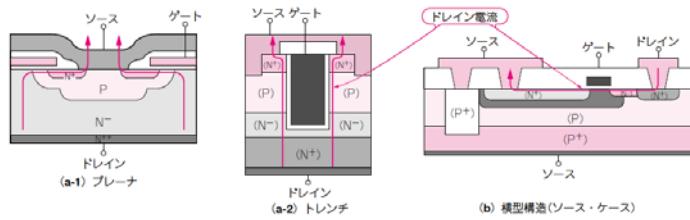

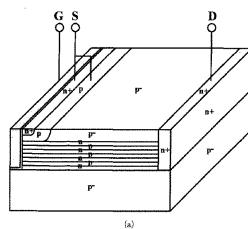

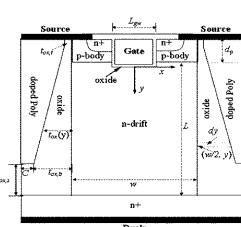

# パワーMOSFETの高性能化 縦型構造と横型構造素子

1セルの構造

(a) 縦型構造(ドレイン・ケース)

図2-2 パワーMOSFETの構造による分類

表2-1 パワーMOSFETの構造とその特徴を活かした応用例

CQ出版トランジスタ技術2004/8

縦横構造の比較

| 構造<br>区分                   | 縦型構造                                                                                           |                       | 横型構造                                                                                                              |     |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|-----|

|                            | 低耐圧(100V以下)<br>ブレーナ                                                                            | 高耐圧<br>(ブレーナ)<br>トレンチ | 低耐圧                                                                                                               | 高耐圧 |

| 高耐圧化                       | —                                                                                              | —                     | ○                                                                                                                 | △   |

| 低ON抵抗化                     | ○                                                                                              | ○                     | △                                                                                                                 | ×   |

| 低 $C_{oss}$ (低 $Q_g$ )     | ○                                                                                              | ○                     | ○                                                                                                                 | ○   |

| 低 $C_{oss}$ (低 $Q_{gtr}$ ) | ○                                                                                              | ○                     | ○                                                                                                                 | ○   |

| 特徴                         | 高耐圧、大電流、低ON抵抗                                                                                  |                       | 高速、高周波特性                                                                                                          |     |

| 応用分野、用途など                  | <ul style="list-style-type: none"> <li>DC-DCコンバータ</li> <li>小型モータ駆動</li> <li>自動車電装機器</li> </ul> |                       | <ul style="list-style-type: none"> <li>AC-DCスイッチング電源</li> <li>UPS電源</li> <li>インバータ</li> </ul>                     |     |

|                            |                                                                                                |                       | <ul style="list-style-type: none"> <li>RFアンプ出力(携帯電話)<br/>(数百MHz～数GHz)</li> <li>高周波電力増幅<br/>(基地局放送機器など)</li> </ul> |     |

2008/11/12

応用電力変換工学

25

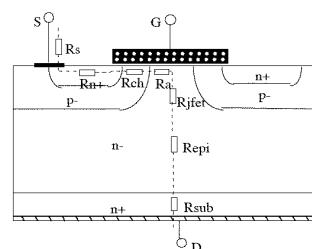

# パワーMOSFETの高性能化

## • 低抵抗化

- 高耐圧素子(100V～)

- エピタキシャル抵抗低減

- 超接合構造

- 低耐圧素子(～100V)

- チャネル抵抗低減

- 微細プロセス化

- » チャネル面積増大

- JFET抵抗低減

- トレンチゲート構造

- » JFET領域消滅

- エピタキシャル抵抗低減

|             | VDS = 30 V | VDS = 600 V |

|-------------|------------|-------------|

| Rs          | 7 %        | 0.5 %       |

| Rn+         | 6 %        | 0.5 %       |

| Rch         | 28 %       | 1.5 %       |

| Ra          | 23 %       | 0.5 %       |

| Rjfer, Repi | 29 %       | 96.5 %      |

| Rsub        | 7 %        | 0.5 %       |

図3. パワーMOSFETのオン抵抗成分比率

菅井,新電元Password Vol.02-16,p.2,2002.

2008/11/12

応用電力変換工学

26

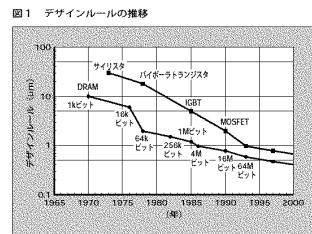

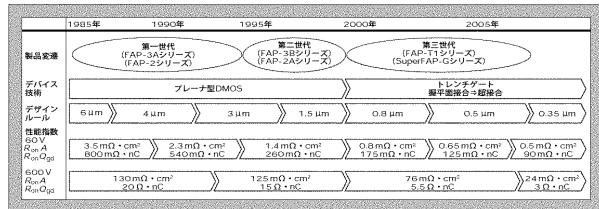

# パワーMOSFETの高性能化 プロセス微細化

- サイリスタ, バイポーラトランジスタ

- 微細化の要求小

- MOSゲートデバイス

- 微細化によるチャネル抵抗低減

- LSIと同等のプロセス・クリーンルームで製造

図1 デザインルールの推移

富士時報

Vol.74, No.2,

p.103, 2001.

富士時報

Vol.77, No.5,

p.309, 2004.

2008/11/12

応用電力変換工学

27

# パワーMOSFETの高性能化 擬平面接合(QPJ: quasi plane junction)

図8 SuperFAP-G系列のナップ構造

富士時報 Vol.79, No.5, p.380, 2006.

2008/11/12

応用電力変換工学

- 通常セル構造

- 三次元的な凹凸

- 高濃度で深いp+ウェル

- 電界の局所集中

- 理論限界の80%耐圧

- 擬平面接合

- 平面に近い接合

- 低濃度で浅いp-ウェル

- 稠密配置

- 電界分布を一様化

- 耐圧向上

- QgdとRdsのトレードオフ改善

- 短い電流経路

28

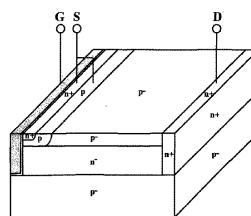

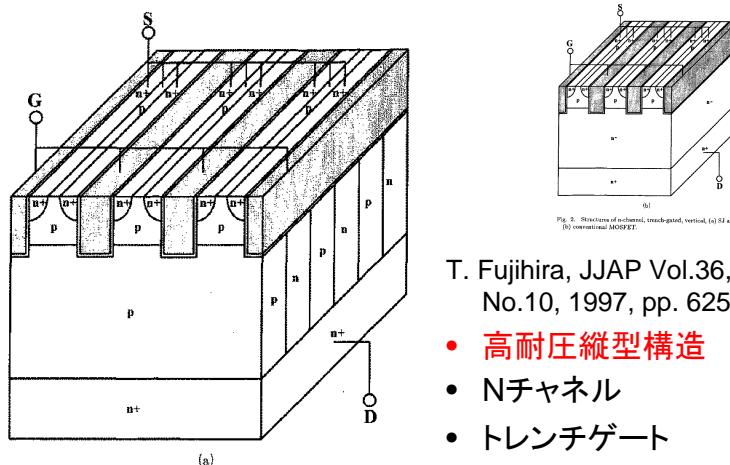

## パワーMOSFETの高性能化 超接合構造

- 耐圧を保持するエピタキシャル層の抵抗が支配的

- 微細加工によるオン抵抗低減の限界

- エピタキシャル層(Nドリフト層)にP型柱を形成

- 埋め込み拡散とエピタキシャル成長の繰り返し

- 阻止時にp層電荷とn層電荷をバランスさせ完全空乏化し、耐圧を得る

- Nドリフト層の微細化により不純物濃度を上げれる

- 低抵抗化が可能

- 接合数に反比例してオン抵抗が下がる

2008/11/12

応用電力変換工学

29

## パワーMOSFETの高性能化 超接合構造

T. Fujihira, JJAP Vol.36, Pt.1,

No.10, 1997, pp. 6255.

- **横型構造**

- **Nチャネル**

- **トレンチゲート**

2008/11/12

応用電力変換工学

30

# パワーMOSFETの高性能化 超接合構造

T. Fujihira, JJAP Vol.36, Pt.1, No.10, 1997, pp. 6255.

- 高耐圧縦型構造

- Nチャネル

- トレンチゲート

2008/11/12

応用電力変換工学

31

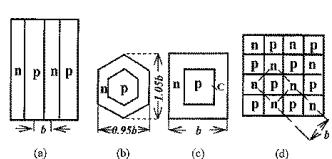

# パワーMOSFETの高性能化 超接合構造の最適化

## • 超接合構造断面最適化

### – 横断面

- (a) 積層構造

- (b) 六角形構造

- (c) 四角形構造

- (d) 市松模様構造

### – 最適電界分布

- 縦方向=横方向電界

- 積層構造は電荷補償効果が1D

- (b)-(d)は2Dで電荷補償効果有り

- (b)が最適

Fig. 2. Different design patterns of the CB-structure. (a) Interdigitated layout. (b) Hexagonal layout. (c) Square layout. (d) Lattice layout.

X. Chen, et.al., "Optimization of the Specific On-Resistance of the COOLMOS™", IEEE ED, Vol.48, No.2, pp.344-348, 2001.

2008/11/12

応用電力変換工学

32

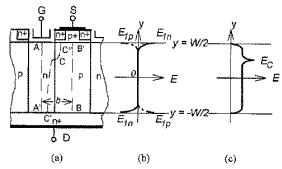

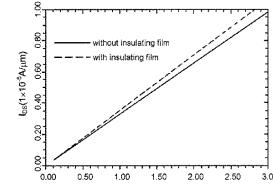

# パワーMOSFETの高性能化 超接合構造の最適化

Fig. 1. Schematic cross-sectional view of an RMOST using the CB-structure concept, and the corresponding field profiles: (a) The structure; (b) field profiles of  $E_1$  along AA' (solid-curve) and along BB' (dashed curve); (c) field profile along a field line passing through point C.

Fig. 3. A thin oxide layer between the n- and p-region of the RMOST (shaded area represents the oxide).

Fig. 4. Simulated J-V characteristics of two 1 KV RMOSTs at  $V_G = 30$  V with (0.5  $\mu$ m) and without the insulating film.

- P柱とN層の間に酸化膜を挿入

- 酸化膜を介して超接合構造が動作

- $R_{on}$ 低下

- N領域上部, P領域底部の不純物濃度を下げて耐圧を上昇させるのと同等の効果

X. Chen, et.al., "Optimization of the Specific On-Resistance of the COOLMOS™"

IEEE ED, Vol.48, No.2, pp.344-348, 2001.

2008/11/12

応用電力変換工学

33

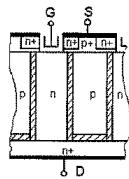

# パワーMOSFETの高性能化 超接合構造 v.s. Oxide bypass構造

- Y.Chen et.al., IEEE PELS, Vol.22, No.4, pp.1303-1310.(2007)

- 超接合構造はp領域の不純物濃度を一様に制御するのが難しい

- 酸化物バイパス(OB)構造

- P柱の変わりに酸化膜使用

- 傾斜構造として電界分布最適化

Fig. 1. Trench gate power NMOS with drift region as: (a) p-n column SJ structure, (b) OB structure, (c) GOB structure.

2008/11/12

応用電力変換工学

34

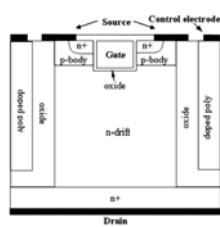

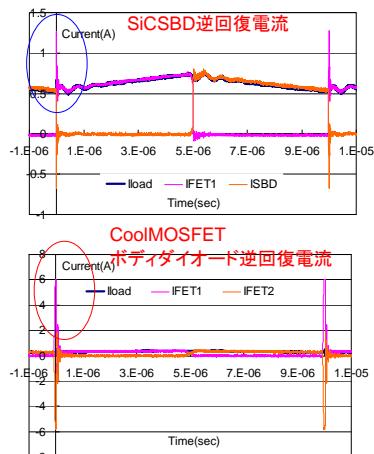

# パワーMOSFETの高性能化 超接合構造のボディダイオード

- 超接合構造の問題

- ドレイン-ソース間のpn接合面積が莫大

- Cds大

- ボディダイオードの逆回復時間が長い

- Cool MOSFETとSiC SBDの組み合わせ

- Z. Liang, et.al., "Integrated CoolMOS FET/SiC-diode module for high performance power switching" IEEE PELS, Vol.20, No.3,679-686, 2005.

2008/11/12

応用電力変換工学

35

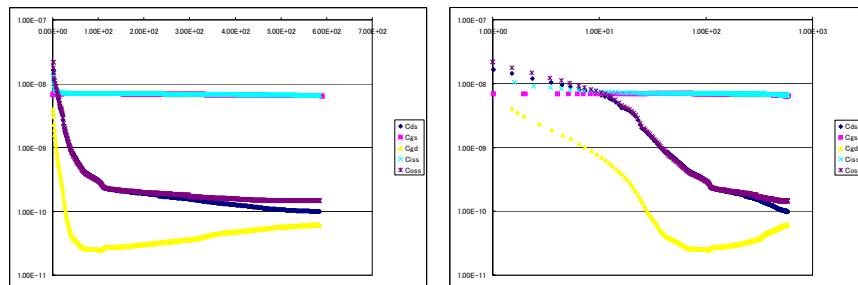

# パワーMOSFETの高性能化 超接合構造の接合容量

Cdsの影響

2008/11/12

応用電力変換工学

36

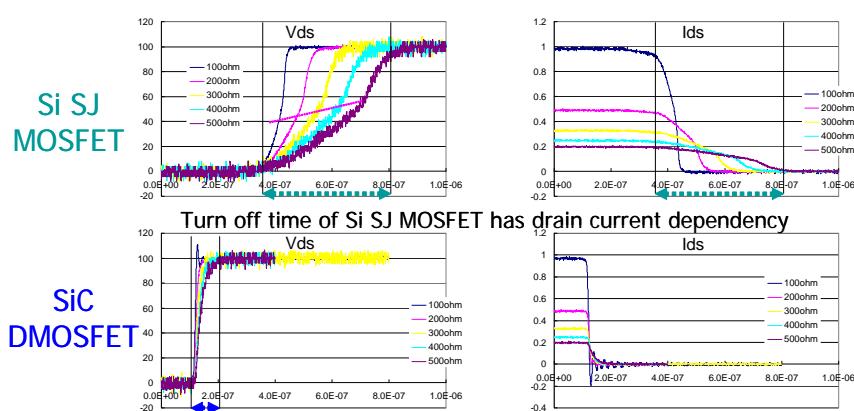

# パワーMOSFETの高性能化 CoolMOSFETの端子間接合容量

片対数表示

両対数表示

2008/11/12

応用電力変換工学

37

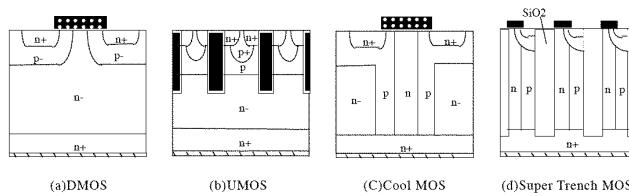

# パワーMOSFETの高性能化 トレンチ構造

図2. パワーMOSFETの各種構造

菅井,新電元Password Vol.02-16,p.2,2002.

- トレンチMOS=UMOS

- チャネルが縦方向に形成される

- 横チャネル時のJFET領域部がなくなる

- ゲート電極がドリフト層と対向する面積を小さくする

- $C_{gd}$ が低下する

- ミラー(Miller)効果が小さくなる

- ゲート駆動損失が小さくなる

2008/11/12

応用電力変換工学

38

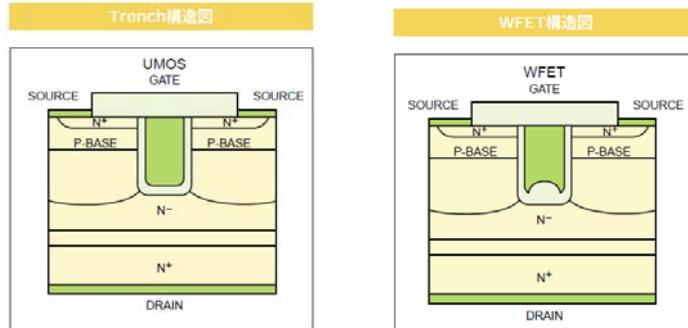

# パワーMOSFETの高性能化 トレンチ構造

VISHAY

Siliconix社

HPより

- WFET

- トレンチの底に厚いゲート酸化膜

- オン抵抗への影響小

- $C_{rss}$ を3分の2削減

- パワーMOSFET遮断周波数

$$f_c \cong \frac{1}{2\pi R_g \{C_{gs} + (1 - A_0)C_{gd}\}}$$

2008/11/12

応用電力変換工学

39

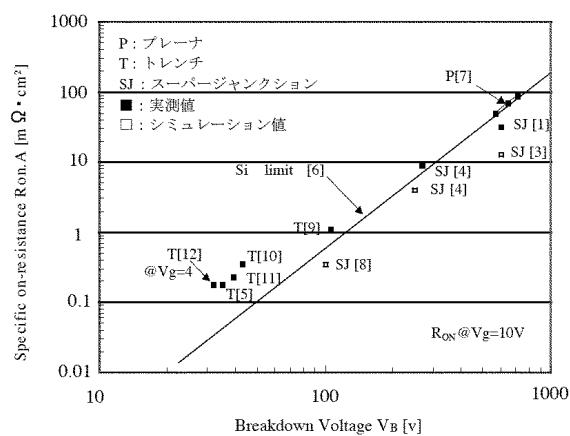

# パワーMOSFETの高性能化 抵抗と耐圧

図4. パワーMOSFETのRonと耐圧

2008/11/12

菅井,新電元Password Vol.02-16,p.3,2002.

応用電力変換工学 40

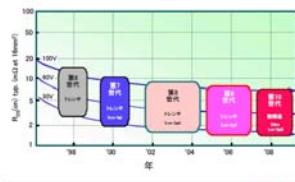

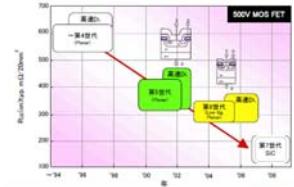

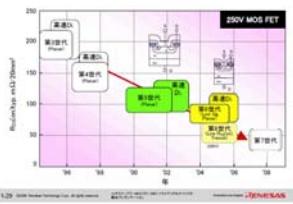

# パワーMOSFETの高性能化

低耐圧パワーMOS FETのオン抵抗性能トレンド

高耐圧パワーMOS FETのオン抵抗性能トレンド

中耐圧パワーMOS FETのオン抵抗性能トレンド

- Power MOSFETの性能指標(FOM)

- $R_{on} \cdot Q_{gd}$

- オン抵抗と高速性を示したパラメータで、オン抵抗( $R_{DS(on)}$ )とゲート・ドレイン電荷量( $Q_{gd}$ )の積。

- ゲート・ドレイン間容量を充放電する電荷量。スイッチング時間に相当。

2008/11/12

応用電力変換工学

41

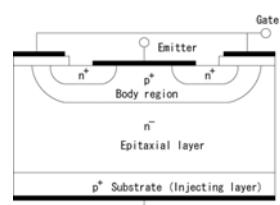

## IGBT (Insulated gate bipolar transistor)

- 高耐圧大電流用

(MOSFETに比べて)

- 導通時

- コレクタ側p+層よりn-層へ少数キャリア注入

- 抵抗低減

- ターンオフ時間とオン電圧のトレードオフ

- ターンオフ時間は注入キャリアの消滅に依存

- ライフタイム制御

- オン電圧の上昇

2008/11/12

応用電力変換工学

42

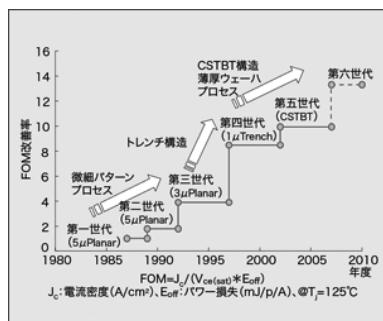

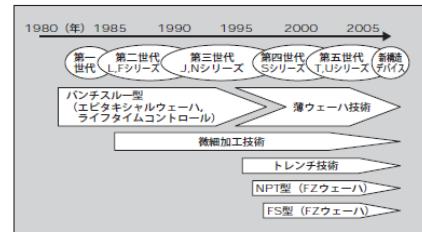

# IGBTの進化

三菱電機(三菱電機技報Vol.81 No.5,2007)

富士電機(富士時報Vol75, No.10,2002)

図1 富士電機製 IGBT の適用技術の推移

ターンオフ時間とオン電圧のトレードオフの改善

- セルピッチの縮小

- トレンチゲート構造の採用

- ライフタイム制御

- ライフタイム制御の改善

- 従来 電子線照射による均一制御

- 新技術 荷電粒子照射による局所制御(プロトン, ヘリウム)

2008/11/12

応用電力変換工学

43

# IGBTの進化

- ライフタイム制御による性能向上

- ライフタイム制御タイプ

- 高注入、低輸送効率

- 非ライフタイム制御タイプ

- 注入効率を抑える

- コレクタからのキャリア注入抑制(注入効率の抑制)

- キャリアの輸送効率向上

- » オン電圧上昇を抑制

- 構造による進化

- パンチスルーライフタイム制御

- エピタキシャルウェーハ

- ライフタイム制御

- 非パンチスルーライフタイム制御

- 空乏層がコレクタに到達しないようドリフト層厚い

- FS (field stop)構造

- N+バッファ層→FS層

- ベース部を薄くする

- 導通時の過剰キャリア少ない

- 空乏層が伸びた状態での中性領域が少ないのでターンオフ損失少ない

2008/11/12

応用電力変換工学

44

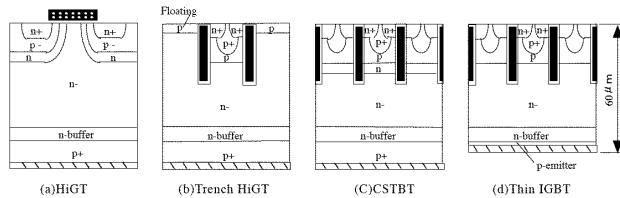

# IGBTの進化

- キャリア分布の改善

- CSTBT (carrier stored trench-gate bipolar transistor)

- IEGT (injection enhanced insulated gate bipolar transistor)

- HiGT (high-conductivity IGBT)

図5. IGBTの各種構造 菅井,新電元Password Vol.02-16,p.4,2002.

応用電力変換工学 45

2008/11/12

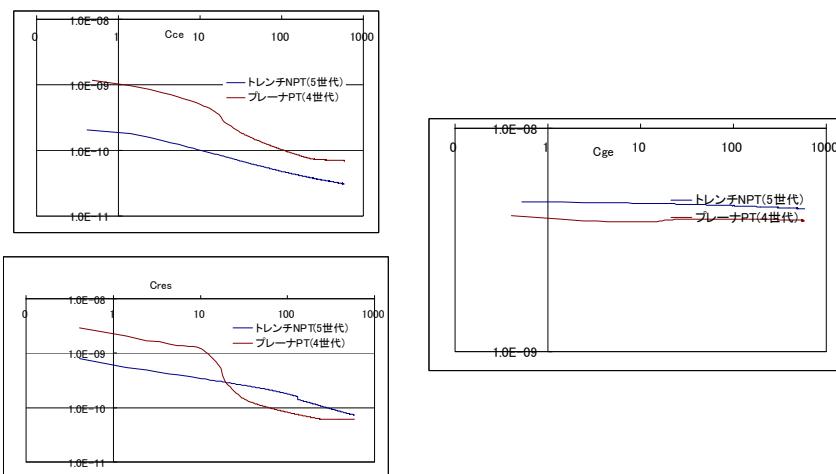

# IGBTの進化 端子間容量

2008/11/12

応用電力変換工学

46

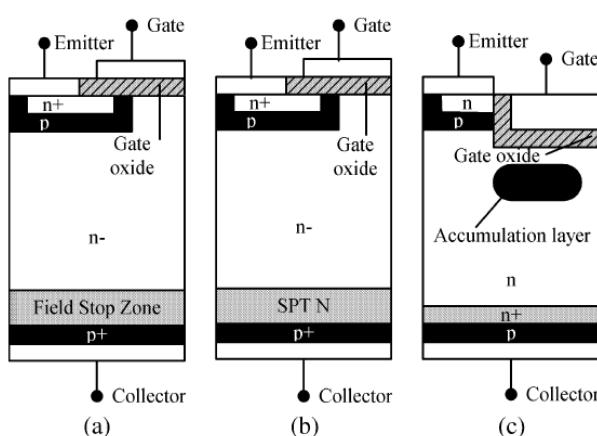

# 高耐圧デバイスとソフトスイッチング

- 高耐圧IGBTのソフトスイッチングへの適合性

- Fujii et.al. "Characterization and comparison of High Blocking Voltage IGBTs and IEGTs Under Hard and Soft switching conditions", IEEE Trans. PELS, vol.23,no.1, pp.172-178 (2008)

- 送配電機器における素子の直列接続数の低減

- 耐圧(順方向電圧降下)とスイッチング損失のトレードオフ

- FS (Field Stop), SPT (Soft punch through), IEGT (Injection enhanced gate transistor)

- 高電圧機器ではハードスイッチングが一般的

- ソフトスイッチングにおけるスイッチングデバイスの振る舞いは?

» ZVS動作への影響

2008/11/12

応用電力変換工学

47

## 高耐圧IGBTの構造

Fig. 1. Device structure. (a) FS-IGBT. (b) SPT-IGBT. (c) IEGT.

出典 Fujii et.al. ,IEEE Trans. PELS, vol.23,no.1, pp.172-178 (2008)

2008/11/12

応用電力変換工学

48

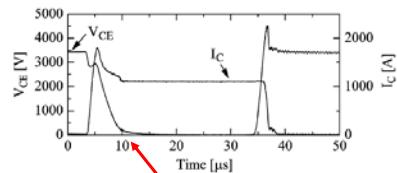

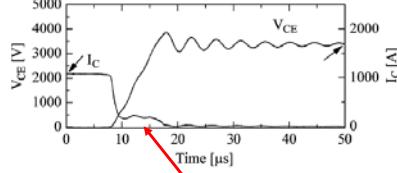

## 高耐圧IGBTでの ハード・ソフトスイッチング波形

### ハードスイッチング波形

Fig. 5. Waveforms of the 6.5-kV SPT-IGBT under hard-switching conditions.

テール電流

### ソフトスイッチング波形

Fig. 10. Waveforms of the 6.5-kV SPT-IGBT under soft-switching conditions

( $C_{r1}, C_{r2} = 1 \mu\text{F}$ ).

テール電流

- ソフトスイッチングのターンオフ損失はテール電流に依存する

- テール電流はターンオフ後の $dv/dt$ に依存する

- ハードスイッチングは $dv/dt$ が大きいのでテール電流が短くなる

出典 Fujii et.al. ,IEEE Trans. PELS, vol.23,no.1, pp.172-178 (2008)

2008/11/12

応用電力変換工学

49

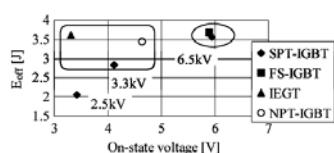

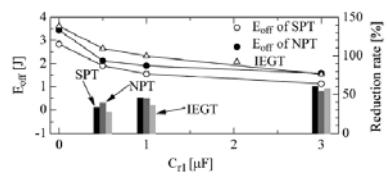

## 高耐圧IGBTのソフトスイッチング損失

### 順方向電圧とスイッチング損失

Fig. 14. On-state voltage and turn-off energy of IGBTs at nominal voltage, current and 120 °C.

### ZVS用コンデンサとスイッチング損失

Fig. 15. Turn-off energy of 3.3-kV devices at 1800 V, 1200 A, and 120 °C.

- IEGTは順方向電圧降下が小さい

- Nベース部に電荷(電子)を蓄積する

- テール電流が長くなる

- スイッチング(ターンオフ)損失が大きい

- 高電圧素子ほどZVS化の効果が大きい

出典 Fujii et.al. ,IEEE Trans. PELS, vol.23,no.1, pp.172-178 (2008)

2008/11/12

応用電力変換工学

50

# RoHS指令 鉛フリー化

- Restriction of Hazardous Substances(危険物質に関する制限)

- 電子・電気機器における特定有害物質の使用制限についての欧州連合(EU)による指令

- 鉛 : 1,000ppm以下

- 適用免除 高温溶接タイプの鉛はんだ

- パワーデバイスのダイボンド

- 鉛フリーはんだ

- 溶融温度が高い(数十度)素子の熱破壊や劣化

- ウィスカ―(針状の金属結晶)が発生による端子間のショート

2008/11/12

応用電力変換工学

51

## おわりに

- アプリケーションに応じたデバイス選定

- 電圧

- 電流

- 速度

- 動作温度

- 素子特性を考慮した回路設計

- ハードスイッチング

- ソフトスイッチング

- 素子特性を支配する要素

- 材料

- Si etc.....

- 基本動作

- ユニポーラ

- バイポーラ

- ドリフト層構造

- 縦型

- 横型

- ゲート構造

- プレーナー

- トレンチ

- パッケージング

デバイス開発はつづくよ何処までも…

回路開発に応じて

2008/11/12

応用電力変換工学

52